## MEDICON MICROBIOLOGY

Volume 1 Issue 4 May 2022

Research Article

## Modelling and Simulation of Hetero-Dielectric Junction-less TFET for Low Power Applications

### Sagarika Choudhury\* and Krishna Lal Baishnab

*Pepartment of Electronics and Communication Engineering, National Institute of Technology, Silchar, Assam, 788010, India*\*Corresponding Author: Sagarika Choudhury, Department of Electronics and Communication Engineering, National Institute of Technology, Silchar, Assam, 788010, India.

Received: April 25, 2022; Published: May 03, 2022

#### Abstract

This paper put forwards afresh concept to improvise the conventional JL-TFET. The choice and placement of dielectric are crucial in determining the efficiency of the device. Thus, asymmetric hetero-dielectric is found to improve the gate control and also aid in lowering capacitance. The concept of triple gate material has been incorporated which resulted in better gate control and thereby improving ON-current. The proposed structure reports a current ratio of  $4.4 \times 10^{10}$ A and promising values for Subthreshold Swing (SS) 9 mV/dec (point) and 48 mV/dec (average). This improvised structure helps in development of devices suitable for low power applications. The simulation based study was performed in July 2021 and compared with the results available.

**Keywords:** TFET; JLTFET; Hetero-dielectric; Asymmetry

#### Introduction

The growth of semiconductor industry has increased many fold in recent decade. Researchers are coming up with many new ideas to outperform the demerits of conventional devices and improve their efficiency. With the ongoing miniaturisation and improvisation, the Junction less devices [1] came into picture to overcome the difficulty of fabricating [2-4] abrupt junctions [5]. Moreover, in recent times TFET [6, 7] is one major replacements for conventional devices specifically for low power applications. JLTFET is basically an amalgamation of two concepts: JLFET with tunnelling phenomenon. It works on the principle of work function modulation [1] wherein a uniformly doped n-type device is made to behave as PIN structure. Moreover, this work also tries to incorporate the advantage of TMG [8-10] for better gate control along with asymmetry for improved performance. With the use of high k near tunnelling junction the electric field [11] across the junction increases, and this in turn increases the tunnelling efficiency, thus ON-current is increased. Similarly, the use of low k near drain resulted in decrease in OFF- current. Hence, it has been observed that the use of TMG with asymmetric hetero-dielectric significantly enhances the current ratio with moderate values for SS. A numerous number of analytical models for junction less TFETs are discussed in various literature [1, 12, and 13]. The simulations are carried out in TCAD simulation tool.

This work has the following sections: starts with describing the device structure, subsequently results are discussed and finally the conclusion section is presented.

#### **Device Structure**

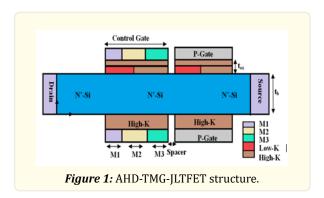

An Asymmetric Hetero-dielectric Triple Material Gate Junction less TFET is proposed. This structure overcomes the drawback of conventional JLTFET by improving the ON- current. Fabricating abrupt junction is quite difficult [12], thus, junction less structures with uniform doping across the device comes to the limelight. The structure is designed on silicon base with uniform doping of 1x10<sup>19</sup> cm<sup>-3</sup>. Moreover, due to incorporation hetero-dielectric in asymmetric technique, low-k material is added across the drain. This in turn results in low capacitance. The asymmetry in the structure improves the gate control capacity. Improved ON-current and low capacitance are the key factors that makes a device ideal for low power applications. Two gates are incorporated in the proposed structure: Polar gate at zero bias for inducing P region and Control gate for inducing channel region by work function variability. The control gate has three metal [14] with different work-function. Each section is labelled as M1, M2, and M3 with length L1, L2 and L3. Synopsis TCAD tool is used to perform all the simulations. The length and other dimensions are listed in table 1.

| Parameters | Values |  |  |

|------------|--------|--|--|

| L1         | 6nm    |  |  |

| L2         | 12nm   |  |  |

| L3         | 6nm    |  |  |

| $t_{oxf}$  | 3nm    |  |  |

| $t_{b}$    | 3nm    |  |  |

Table 1: Dimension of device.

# Results and discussion Device Characteristics

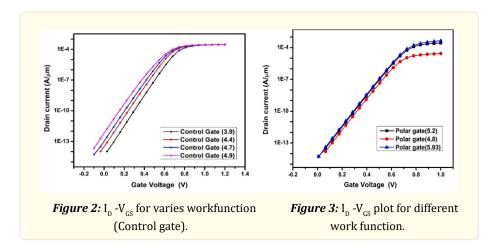

Figure 2 portrays the study of work function variability of control gate. An On-current of  $4.4 \times 10^{-4}$  A and OFF-current of  $1 \times 10^{-14}$  A for control gate work function of 5.93 eV is found. However, the Polar gate work function significantly impacts the polarization charge in the source region. With increase in the work function the bands move up, effective tunnel width increases in the tunnel junction, thereby, it increases ON current while keeping OFF current in permissible limit. Thus, Polar work function of 5.93 eV modulates the carrier density below the gate and helps in achieving the best current ratio as depicted in fig 3.

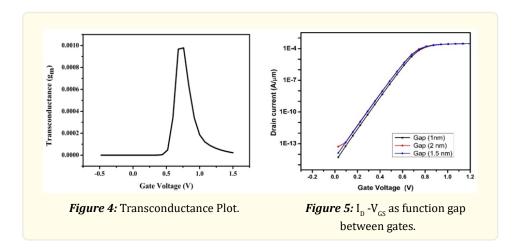

Moreover, physical renovation also resulted in improved SS average. The values obtained for Subthreshold Swing (SS) are 9 mV/dec (Point) and 48 mV/dec (Average). The average SS is calculated by calculating minimum and threshold voltages. Thus, to calculate the threshold voltage the current is kept constant. At a constant current of  $1x10^8$ A/ $\mu$ m, the threshold voltage of 0.34 is obtained. The leakage current and SS value also reflects much improvement. The analog performance depends substantially on the transconductance of the device defined by the formula stated in equation (1). Fig.4, reports the  $g_m$  of the AHD-TMG-JLTEFT as  $1 \times 10^{-3}$  S/ $\mu$ m and it is reasonably greater than reported JLTFET's.

$$g_{m} = \frac{dI_{D}}{dV_{gs}} \tag{1}$$

The gap between the gates is another important parameters impacting the fringe field effect in the device. Increasing the gap between the gates increases the OFF-current. Fig 5 shows that a gap of 1nm gives the best current ratio.

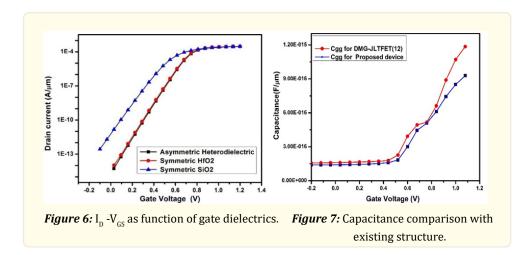

The gate dielectric also modulates the device performance. Symmetric dielectric (SiO<sub>2</sub>) has much higher OFF-current as shown in fig 6. An asymmetric hetero-dielectric provides the best current ratio.

| $I_{oN}(A/\mu m)$      | $I_{OFF}$ (A/ $\mu$ m) | Ratio                 | $V_{th}(V)$ | SS (Average) | SS (Point) | References    |

|------------------------|------------------------|-----------------------|-------------|--------------|------------|---------------|

| 36x10 <sup>-6</sup>    | 5x10 <sup>-14</sup>    | 6x10 <sup>8</sup>     | 0.4         | 70           | 38         | Ref [1]       |

| 18x10 <sup>-5</sup>    | 3x10 <sup>-13</sup>    | 6x10 <sup>8</sup>     | 0.4         | -            | 17         | Ref [12]      |

| 1x10 <sup>-6</sup>     | 1x10 <sup>-13</sup>    | 6x10 <sup>7</sup>     | 0.8         | 48           | -          | Ref [14]      |

| 4.4 x 10 <sup>-4</sup> | 1 x 10 <sup>-14</sup>  | 4.4 x10 <sup>10</sup> | 0.34        | 48           | 9          | Proposed work |

Table 2: Showing the comparison with reference works.

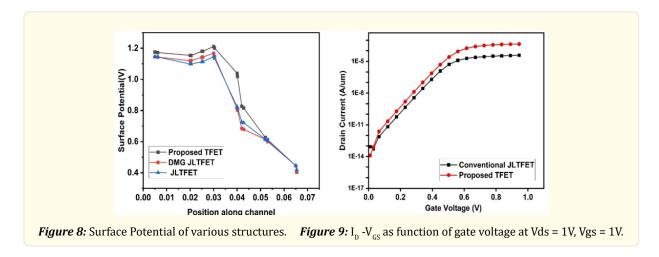

The table 2 portrays the comparison amongst various junction less devices proposed in the literature. The structure shows massive improvement in SS values along with current ratio proving the utility of the device. The capacitances are computed at a frequency of 1MHz. Due to usage of asymmetric dielectric the total gate capacitance of TMG-AHD JLTEFET is lower compared to conventional DMG-JLTFET [15]. Again, a plot depicting comparison amongst various junction less structures in terms of surface potential is shown in fig.8. The surface potential is a significant device parameter for analysing device performance. Since, with increase in surface potential the electric field also improvises at the junction, thereby increasing tunnel efficiency. The step profile of surface potential is as a result of the use of three different gate material. It has been observed that the rate of variation is slightly elevated across drain junction due to certain assumptions made while developing the model. Furthermore, the comparison with conventional JLTFET is shown in fig. 9.

#### Conclusion

A detailed study of the proposed structure is performed by analytical modelling and simulating the device in TCAD software. It is observed that the performance of this conventional JLTFET can be improvised by using asymmetric combination of high k and low k dielectric. The performance of the proposed device is found to be suitable for low power applications. Moreover the performance achieved is compared with the existing structure present in the literature. It has been observed that the proposed structure shows improvement in current ratio as well as SS which makes it an adroit candidate for low power application. Thus, this Si based device reports an improved ON-current of  $4.4 \times 10^{-4}$  A, OFF current of  $1 \times 10^{-14}$  A. and current ratio of  $4.4 \times 10^{10}$  and SS value 9 mV/dec (point) and 48 mV/dec (average).

#### References

- 1. B Ghosh and MW Akram. "Junctionless Tunnel Field Effect Transistor". IEEE Electron Device Lett 34.5 (2013): 584-586.

- 2. EH Toh., et al. "Performance enhancement of n-channel impact-ionization metal-oxide- semiconductor transistor by strain engineering". Appl. Phys. Lett (2007).

- 3. N Damrongplasit, SH Kim and TJK Liu. "Study of random dopant fluctuation induced variability in the raised-ge-source TFET". IEEE Electron Device Lett (2013).

- 4. S Gundapaneni., et al. "Effect of band-to-band tunneling on junctionless transistors". IEEE Trans. Electron Devices (2012).

- 5. Y Pratap., et al. "Gate-Material-Engineered Junctionless Nanowire Transistor (JNT) with Vacuum Gate Dielectric for Enhanced Hot-Carrier Reliability". IEEE Trans. Device Mater. Reliab (2016).

- 6. KK Bhuwalka, J Schulze and I Eisele. "Scaling the Vertical Tunnel FET with Tunnel Bandgap Modulation and Gate Workfunction Engineering". IEEE Transactions on Electron Devices 52.5 (2005): 909-917.

- 7. KK Bhuwalka., et al. "P-channel tunnel field-effect transistors down to sub-50 nm channel lengths". Japanese J. Appl. Physics, Part 1 Regul. Pap. Short Notes Rev. Pap (2006).

- 8. N Bagga., et al. "An Analytical Model for Tunnel Barrier Modulation in Triple Metal Double Gate TFET". IEEE Trans. Electron Devices 62.7 (2015): 2136-2142.

- 9. P Vanitha, NB Balamurugan and GL Priya. "Triple Material Surrounding Gate (TMSG) Nanoscale Tunnel FET-Analytical Modeling and Simulation". Journal of Semiconductor Technology and Science 15.6 (2015): 585-593.

- 10. MI Dewan, T Bin Kashem, and S Subrina. "Characteristic Analysis of Triple Material Tri-Gate Junctionless Tunnel Field Effect Transistor". 2016 9th Int. Conf. Electr. Comput. Eng (2016): 333-336.

- 11. MA Raushan, N Alam and MJ Siddiqui. "Performance Enhancement of Junctionless Tunnel Field Effect Transistor Performance Enhancement of Junctionless Tunnel Field Effect Transistor Using Dual-k Spacers". Journal of Nanoelectronics and Optoelectronics (2018).

- 12. P Bal., et al. "Dual material gate junctionless tunnel field effect transistor". Journal of Computational Electronics 13.1 (2014): 230-234.

- 13. MW Akram., et al. "P-type double gate junctionless tunnel field effect transistor". Journal of Semiconductors 35.1 (2014): 1-7.

- 14. SK Gupta and S Kumar. "Analytical Modeling of a Triple Material Double Gate TFET with Hetero-Dielectric Gate Stack". Silicon 11.3 (2019): 1355-1369.

- 15. S Darwin and ASTS. "Mathematical Modeling of Junctionless Triple Material Double Gate MOSFET for Low Power Applications". Journal of Nano Research 56 (2019): 71-79.

- 16. GL Priya and NB Balamurugan. "New dual material double gate junction less tunnel FET: Subthreshold modeling and simulation". AEU International Journal of Electronics and Communications 99 (2019): 130-138.

#### Volume 1 Issue 4 May 2022

© All rights are reserved by Sagarika Choudhury., et al.